CPU (SOC) 的原理与制作

cpu的制作对计算机原理,底层编译原理,内存操作,操作系统原理等很有帮助,从原理上解决计算机的问题

通过硬件上的描述解释软件上的一些问题

一,soc制作的开始

soc称为系统级芯片,也有称片上系统,意指它是一个产品,是一个有专用目标的集成电路,其中包含完整系统并有嵌入软件的全部内容

同样的,soc包括很多部分,最主要的部分分为几个部分,由运算器,控制器,寄存器,内部总线等部件组成,soc的程序可以加入Rom里面的

一个完整的8bit soc长成这种样子

soc不止由硬件上构成,我们的逻辑运算都是通过不同的逻辑电路实现的,而我们的cpu的启动是靠一些高低电平,高电平是1,低电平是0,而让cpu执行运算的部分是alu,而执行一系列操作的东西是指令集,让cpu动起来的是时钟,下面是本次设计的cpu的范例程序:

二,逻辑电路基础

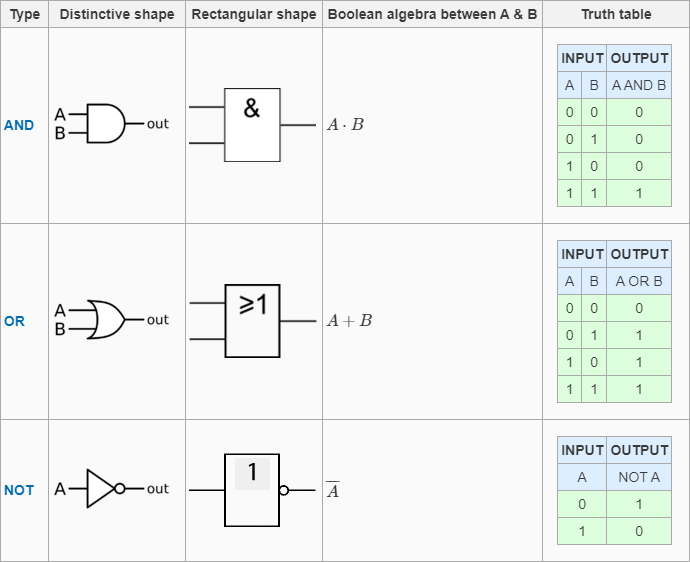

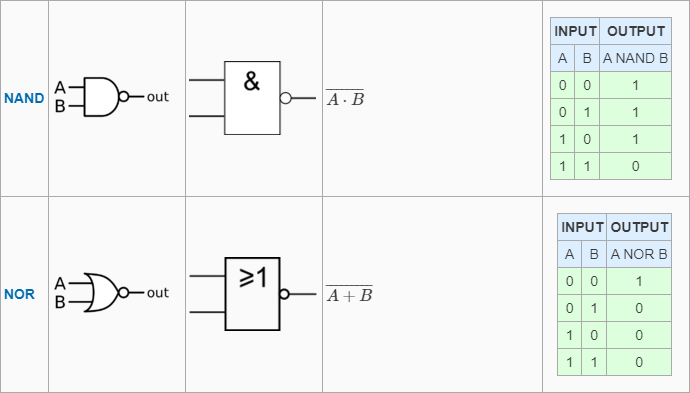

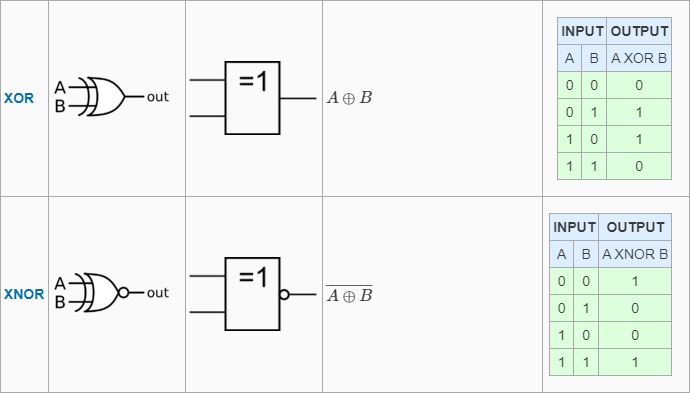

逻辑电路是最基本的电子电路,是所有数字电路的基础。

电脑能够精确、高速的进行各种处理和复杂运算,其运算系统是由许多复杂电路构成的,这些复杂电路的基本组成是逻辑电路,数字电路就是由逻辑电路组成。

以下为一些经典的门电路

-

与门 AND

-

或门 OR

-

非门 NOT

-

与非门 NAND

-

或非门 NOR

-

异或门 XOR

-

同或门 XNOR

通过对门电路的认知了解最基本的门电路与数电原理。

三,soc的制作

我们要实现的是一个基于mips指令集的CPU,并且我们最后要自己为这个CPU设计指令并且编码

1,CPU的诞生

日本客户希望英特尔帮助他们设计和生产八种专用集成电路芯片,用于实现桌面计算器。英特尔的工程师发现这样做有两个很大的问题。

第一,英特尔已经在全力开发 三种内存芯片了,没有人力再设计八种新的芯片。

第二,用八种芯片实现计算器,将大大超出预算成本。

英特尔的一个名叫特德·霍夫(Ted Hoff)的工程师仔细分析了日本同行的设计,他发现了一个现象。这八块芯片各实现一种特定的功能。当用户使用计算器时,这些功能并不是同时都需要的。比如,如果用户需要计算100个数的和,他会重复地输入一个数,再做一次加法,一共做100次,最后再打印出来。负责输入、加法和打印的电路并不同时工作。 这样,当一块芯片在工作时,其他芯片可能是空闲的。

霍夫有了一个想法:为什么不能用一块通用的芯片加上程序来实现几块芯片的功能呢?当需要某种功能时,只需要把实现该功能的一段程序代码(称为子程序)加载到通用芯片上,其功能与专用芯片会完全一样。

经过几天的思考后,霍夫画出了计算器的新的体系结构图,其中包含4块芯片:

一块通用处理器芯片,实现所有的计算和控制功能;

一块可读写内存(RAM)芯片, 用来存放数据;

一块只读内存(ROM)芯片,用来存放程序;

一块输入输出芯片,实现键入数据和操作命令、打印结果等等功能。

这样就做成了一种款式的cpu,同样的我们也可以知道CPU是一种用来代替专用集成电路的器件,说清楚一些就是大规模集成电路,就像密闭的pcb板子一样

2,CPU的体系和构架

我们把指令当作是有顺序开关,0关,1开,CPU架构是cpu厂商给属于同一系列的CPU产品定的一个规范,主要目的是为了区分不同类型CPU的重要标示

冯·诺伊曼结构

冯·诺伊曼结构也称普林斯顿结构,是一种将程序指令存储器和数据存储器合并在一起的电脑设计概念结构。

哈佛结构

哈佛结构是一种将程序指令储存和数据储存分开的存储器结构。中央处理器首先到程序指令储存器中读取程序指令内容,解码后得到数据地址,再到相应的数据储存器中读取数据,并进行下一步的操作

3,指令集架构(ISA,Instruction Set Architecture)

ISA 作为处理器与软件之间的接口,规定了处理器可以执行的指令集合,涵盖了各种操作,例如加法和乘法。这些指令明确定义了机器指令的格式、编码方式以及对应的操作,例如处理包含 32 位小数的数字。

不同的 ISA 会对软件的兼容性和性能产生影响。如果软件是为特定的指令集编写的,那么它可以在任何支持该指令集的 CPU 上运行,无需修改代码。

4,指令集与微架构的关系:

CPU 的微架构负责将指令集中的指令翻译成微操作,这些微操作在处理器内部执行。微架构的设计直接塑造了 CPU 的性能,更为高效的微架构能够提升指令执行速度并提高能效。

CPU 厂商在不改变指令集的前提下,可以通过升级或迭代微架构,来提升性能、能效或其他特性。在实际应用中,了解两者的关系有助于更深入地理解处理器的运行机制。

如今,主流 ISA 只有少数几种,其中主要包括:

| 指令集 | 类型 | 拥有者 | 主要应用 |

|---|---|---|---|

| x86 | CISC | Intel 和 AMD | 个人电脑、服务器、游戏主机 |

| ARM | RISC | Arm | 移动设备、嵌入式系统 |

| RISC-V | RISC | 开放标准 | 个人电脑、服务器、嵌入式系统 |

| PowerPC | CISC | IBM | 数据中心、游戏主机 |

| MIPS | RISC | Imagination Technologies | 处理器、嵌入式系统 |

| Alpha | CISC | DEC | 服务器、工作站 |

| PA-RISC | CISC | HP | 服务器、工作站 |

| SuperH | RISC | Hitachi | 嵌入式系统 |

| 68000 | CISC | Motorola | 游戏主机、嵌入式系统 |

微架构方面至少有数百种,甚至更多。常见的有:

| 微架构 | 指令集 | 拥有者 | 主要应用 | 特点 |

|---|---|---|---|---|

| Zen | x86 | AMD | 个人电脑、服务器 | 多核设计、高性能、高能效 |

| Lake | x86 | Intel | 个人电脑、服务器 | 混合式架构、高性能、低功耗 |

| Cortex | ARM | Arm | 移动设备、嵌入式系统 | 低功耗、高性能 |

| MIPS32/MIPS64 | MIPS | Imagination Technologies | 处理器、嵌入式系统 | 高性能、高扩展性 |

| POWER4/5/9 | PowerPC | IBM | 数据中心、游戏主机 | 高性能、高可靠性 |

| Cortex-M | ARM | Arm | 嵌入式系统 | 低功耗、低成本 |

| RV32I/RV64I | RISC-V | 开放标准 | 嵌入式系统 | 简单、低功耗 |

| Cascade Lake | x86 | Intel | 服务器 | 高性能、高可靠性 |

| Neoverse | ARM | Arm | 高性能计算 | 高性能、高能效 |

| Ethos-U | ARM | Arm | 人工智能 | 高性能、低功耗 |

| AI | RISC-V | 开放标准 | 人工智能 | 简单、低功耗 |

| TPU | 人工智能 | 高性能、高能效 |

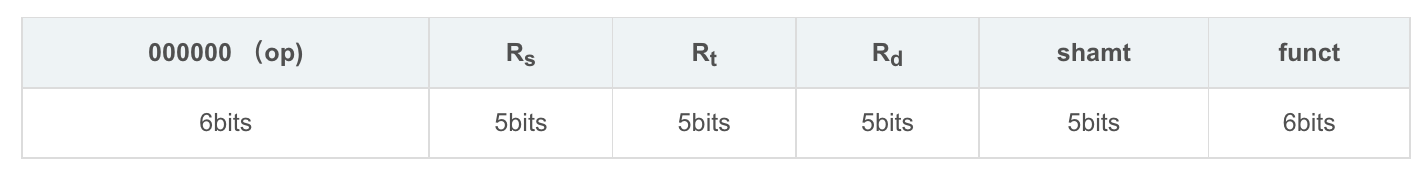

cpu的指令集是一系列的数字集合,下面以mips为主解说:

MIPS架构20多年前由斯坦福大学开发,是一种简洁、优化、具有高度扩展性的RISC架构。它的基本特点是:包含大量的寄存器、指令数和字符、可视的管道延时时隙,这些特性使MIPS架构能够提供最高的每平方毫米性能和当今SoC设计中最低的能耗

rs(Source Register) 通常用于指定第一个源操作数所在的寄存器编号

rt (Target Register) 通常用于指定第二个源操作数所在的寄存器编号

rd (Destination Register)通常用于指定目的操作数(保存运算结果)的寄存器编号

R型指令

R型指令的计算和保存全部都在寄存器进行

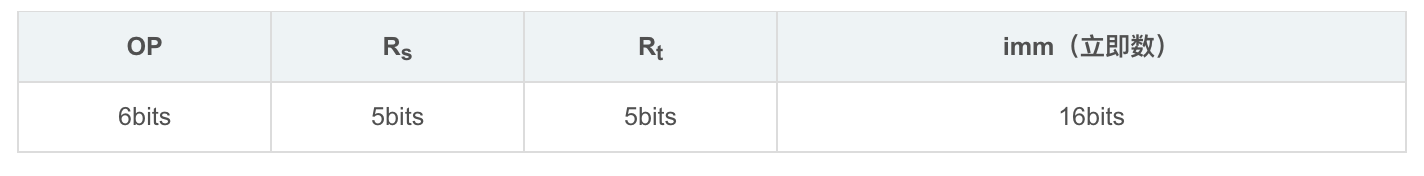

I型指令

操作数中涉及立即数,结果保存到寄存器

J型指令

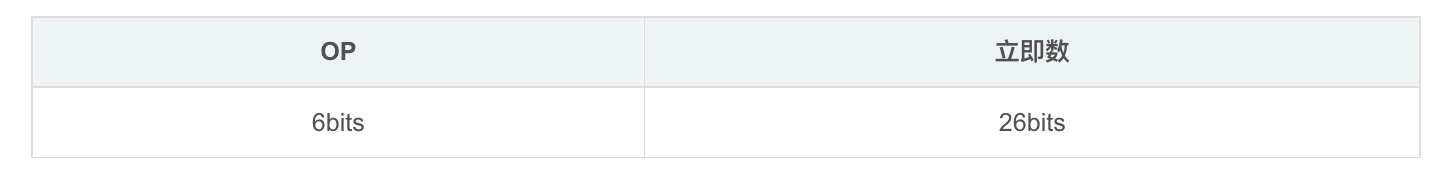

j型是跳转类型的

根据mips指令集模式,我们可以来写出我们自己的指令集